# Border trap analysis and reduction in ALD-high-k InGaAs gate stacks

Kechao Tang<sup>1</sup>, Adi Negara<sup>1</sup>, Tyler Kent<sup>2</sup>, Ravi Droopad<sup>3</sup>, Andrew C. Kummel<sup>2</sup>, and Paul C. McIntyre<sup>1</sup>

<sup>1</sup>Department of Materials Science and Engineering, Stanford University, Stanford, CA 94305

<sup>2</sup>Department of Chemistry and Biochemistry, University of California, San Diego, La Jolla, CA 92093

<sup>3</sup> Ingram School of Engineering, Texas State University, San Marcos, TX 78666

E-mail address of corresponding author: pcml@stanford.edu

For future high performance III-V n-channel MOS devices,  $In_{0.53}Ga_{0.47}As$  is a promising material for the channel due to its high electron mobility and moderate band gap. Atomic layer deposited (ALD)  $Al_2O_3$  has a large conduction band offset to InGaAs and can form a low defect-density interface with InGaAs [1]. ALD-HfO<sub>2</sub> can achieve a very low EOT and low gate leakage [2]. Therefore, both of these oxides have received extensive attention as candidate dielectric layers for InGaAs nMOSFETs. Apart from the well-known effects of oxide/InGaAs interface charge traps that may pin the Fermi level of the channel, traps in the oxide layer, often called border traps, may also reduce the charge in the channel and thus degrade the on-state performance of InGaAs MOSFET devices. In this presentation, we study the effects of various approaches to reduce the border traps, like variation of ALD temperature, post-gate metal forming gas (5% H<sub>2</sub>/95% N<sub>2</sub>) anneals (FGA), and bias-temperature electrical stress.

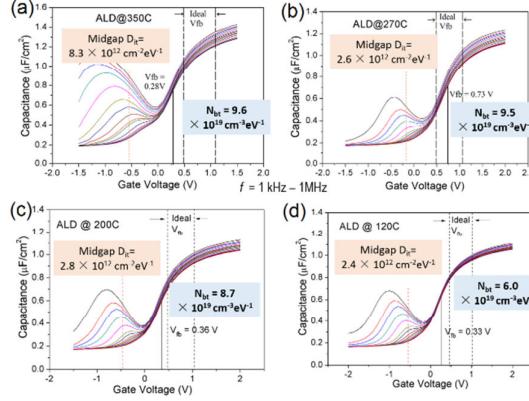

Experimental methods employed include quantitative interface trap and oxide trap modeling [3, 4] of MOS capacitor data obtained over a range of frequencies and temperatures. With the application of these models, we find that the border trap density ( $N_{bt}$ ) in ALD  $Al_2O_3$  depends strongly on ALD temperature. Fig. 1 shows the multi-frequency CV curves for post-metal FGA treated Pd/ $Al_2O_3$ /InGaAs samples in which the gate dielectric was deposited at different ALD temperatures. MOS capacitors fabricated using trimethylaluminum (TMA)/H<sub>2</sub>O at an ALD temperature of 120°C have a considerably lower  $N_{bt}$  while maintaining a similarly low interface trap density ( $D_{it}$ ) compared to samples prepared with a more standard 270°C  $Al_2O_3$  ALD temperature. Large-dose TMA exposure (pre-dosing) prior to  $Al_2O_3$  ALD is also found to be an important step to guarantee stable electrical quality of the low temperature-deposited samples.

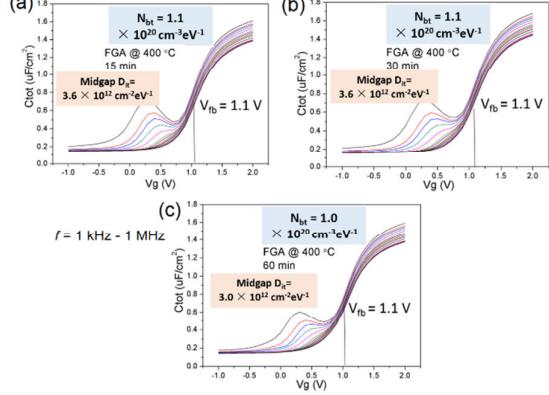

Considering other possible defect passivation approaches, we carry out a systematic study of the effects of post-gate forming gas anneal (FGA) time and temperature on the density of interface and border traps in  $Al_2O_3$ /InGaAs gate stacks. It is found that FGA at 400°C for 30 min saturates the effect of FGA on  $Al_2O_3$ /InGaAs. Fig. 2 shows that increasing the FGA time slightly reduces the  $D_{it}$ , but has little effect on the  $N_{bt}$ . In addition, preliminary results on the effects of bias-temperature stress on  $Al_2O_3$ /InGaAs will be reported.

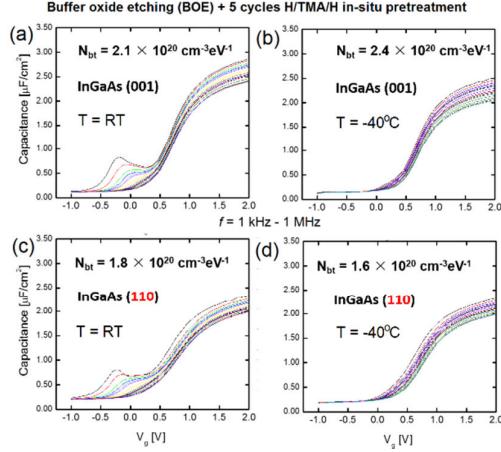

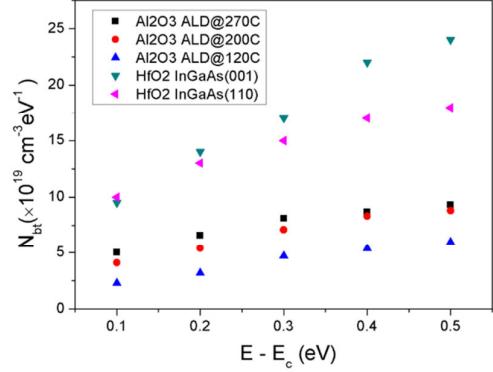

For the ALD-HfO<sub>2</sub> MOS structures, we examine the dependence of  $D_{it}$  and  $N_{bt}$  on 1) the InGaAs surface orientation, 2) HfO<sub>2</sub> ALD temperature, and different substrate surface treatment procedures. Fig. 3 demonstrate that for ALD HfO<sub>2</sub> on both InGaAs (001) surface and (110) surface, the  $D_{it}$  response decreases dramatically when the measurement temperature is lowered from room temperature to -40°C, while the  $N_{bt}$  shows little variations. This result indicates that interface traps and border traps are two different types of defects, which is also supported by another experiment in which we found that increasing the cycle number of in-situ plasma H/TMA/H [5] cleaning cycles prior to HfO<sub>2</sub> ALD significantly reduces the  $D_{it}$  but has little impact on  $N_{bt}$ . In addition, we systematically compared the  $N_{bt}$  of HfO<sub>2</sub> to that of ALD  $Al_2O_3$ . Fig. 4 displays the energy distribution of  $N_{bt}$  in the HfO<sub>2</sub> and  $Al_2O_3$  layers investigated in this study. Comparing each of the dielectrics we have studied, HfO<sub>2</sub> has an  $N_{bt}$  value that is ~3 times larger than that of  $Al_2O_3$ .

In conclusion, we have found that  $Al_2O_3$  deposited on InGaAs with lower ALD temperature has significantly reduced  $N_{bt}$ , and the  $N_{bt}$  of HfO<sub>2</sub> is around 3 times larger than that of  $Al_2O_3$ . The  $N_{bt}$  of HfO<sub>2</sub> is independent of measurement temperature, similar to our previous result on  $Al_2O_3$ /InGaAs gate stacks. Our current work focuses on understanding the physical mechanism under the ALD temperature effect on the  $N_{bt}$  of  $Al_2O_3$ .

## References

- [1] J. Ahn, et al., *Appl. Phys. Lett.* 103 (2013), 071602

- [2] V. Choppattana et al., *J. Appl. Phys.* 114 (2013), 154108

- [3] H. Chen et al., *IEEE TED* 59 (2012), 2383-2389

- [4] Y. Yuan et al., *IEEE TED* 59 (2012), 2100-2106

- [5] V. Choppattana et al., *Appl. Phys. Lett.* 102 (2013), 022907

Fig. 1: Multi-frequency (1 kHz – 1 MHz) CV curves for Pd/Al<sub>2</sub>O<sub>3</sub>/InGaAs samples with Al<sub>2</sub>O<sub>3</sub> ALD temperature at (a) 350°C, (b) 270°C, (c) 200°C and (d) 120°C respectively. D<sub>it</sub> is extracted [3] at energy level of E – E<sub>c</sub> = -0.45 eV, and N<sub>bt</sub> is extracted [4] at energy level of E – E<sub>c</sub> = 0.50 eV.

Fig. 3 : Multi-frequency (1 kHz – 1 MHz) CV curves for HfO<sub>2</sub>/InGaAs MOS capacitors with InGaAs(001) (a - b) and InGaAs(110) (c - d) orientations at room temperature and -40°C. N<sub>bt</sub> is extracted at energy level of E – E<sub>c</sub> = 0.50 eV.

Fig. 2: Multi-frequency (1 kHz – 1 MHz) CV curves for Pd/Al<sub>2</sub>O<sub>3</sub>/InGaAs gate stacks with different FGA time. N<sub>bt</sub> is extracted at energy level of E – E<sub>c</sub> = 0.50 eV.

Fig. 4: Energy distribution of N<sub>bt</sub> for Al<sub>2</sub>O<sub>3</sub> on InGaAs with various ALD temperatures and HfO<sub>2</sub> deposited on InGaAs of different surface orientations.